An L1 Cache with coherence protocol and replacement policy. More...

#include <cache.h>

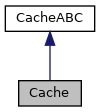

Inheritance diagram for Cache:

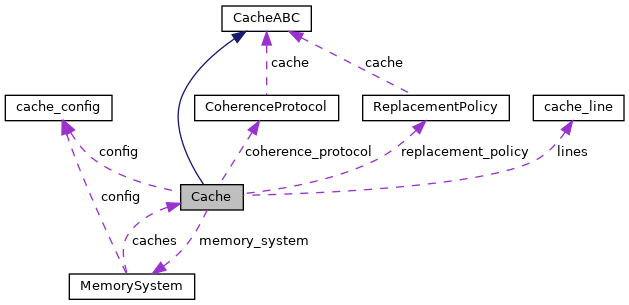

Collaboration diagram for Cache:

Public Member Functions | |

| Cache (MemorySystem &memory_system, uint32_t cache_id, cache_config &config) | |

| Construct a new cache. More... | |

| void | receivePrRd (addr_t addr) |

| Issue a PrRd message to this cache. More... | |

| void | receivePrWr (addr_t addr) |

| Issue a PrWr message to this cache. More... | |

| bool | issueBusMsg (bus_msg_e bus_msg) |

| Issue a BusRd message to neighboring caches. More... | |

| void | receiveBusMsg (bus_msg_e bus_msg, addr_t addr) |

| Issue a bus message to this cache. More... | |

| state_e | getLineState (uint32_t set_idx, uint32_t way_idx) |

| Get the state of a line in the cache. More... | |

| size_t | getTimestamp (addr_t addr) |

| Get the access number of the most recent edit to a cache line. More... | |

| void | printStats () |

| Print simulation run statistics in CSV format (headerless) More... | |

Private Member Functions | |

| void | stateChangeStatistic (state_e before, state_e after) |

| Update the correct state transition statistic. More... | |

| cache_line * | allocate (addr_t addr) |

| Initialize a line in the cache, performing a writeback if necessary. More... | |

| cache_line * | findLine (addr_t addr) |

| Locate a line in the cache. More... | |

Private Attributes | |

| MemorySystem & | memory_system |

| Parent memory system. | |

| cache_config & | config |

| Config from the parent memory system. | |

| CoherenceProtocol * | coherence_protocol |

| Coherence protocol used by this cache. | |

| ReplacementPolicy * | replacement_policy |

| Replacement policy used by this cache. | |

| cache_line * | lines |

| Cache lines contained in this cache. | |

| uint32_t | cache_id |

| ID of this cache. | |

| uint32_t | num_sets |

| The number of sets in the cache. | |

| uint32_t | line_offset |

| Number of bits that come before the line offset field. | |

| uint32_t | tag_offset |

| Number of bits that come before the tag field. | |

| size_t | statistics [N_STATISTICS] = { 0 } |

| Cache runtime statistics. | |

| addr_t | curr_access_addr |

| The address being accessed by the current processor read or write. More... | |

Detailed Description

An L1 Cache with coherence protocol and replacement policy.

Constructor & Destructor Documentation

◆ Cache()

| Cache::Cache | ( | MemorySystem & | memory_system, |

| uint32_t | cache_id, | ||

| cache_config & | config | ||

| ) |

Construct a new cache.

- Parameters

-

memory_system The parent memory system cache_id The ID of this cache config The configuration of the parent memory system

Member Function Documentation

◆ allocate()

|

private |

Initialize a line in the cache, performing a writeback if necessary.

- Parameters

-

addr The address that requires caching

- Returns

- A pointer to the newly initialized cache line

- Note

- The line's state will be 'Invalid'

◆ findLine()

|

private |

Locate a line in the cache.

- Parameters

-

addr The address being accessed

- Returns

- A pointer to the line if found, else nullptr

◆ getLineState()

|

virtual |

Get the state of a line in the cache.

- Parameters

-

set_idx The index of the set containing the line way_idx The index of the way containing the line (0 to assoc-1)

- Returns

- The state of the cache line

Implements CacheABC.

◆ getTimestamp()

| size_t Cache::getTimestamp | ( | addr_t | addr | ) |

Get the access number of the most recent edit to a cache line.

- Parameters

-

addr The address to ckeck

- Returns

- The timestamp of the cache line if the address is in the cache, otherwise 0

◆ issueBusMsg()

|

virtual |

Issue a BusRd message to neighboring caches.

- Parameters

-

bus_msg The specific bus message

- Returns

- True if the 'COPIES-EXIST' line was asserted

Implements CacheABC.

◆ printStats()

| void Cache::printStats | ( | ) |

Print simulation run statistics in CSV format (headerless)

- Note

- Does not produce output if the cache is unused

◆ receiveBusMsg()

Issue a bus message to this cache.

- Parameters

-

bus_msg The specific bus message addr The address accessed

◆ receivePrRd()

| void Cache::receivePrRd | ( | addr_t | addr | ) |

Issue a PrRd message to this cache.

- Parameters

-

addr The address accessed

◆ receivePrWr()

| void Cache::receivePrWr | ( | addr_t | addr | ) |

Issue a PrWr message to this cache.

- Parameters

-

addr The address accessed

◆ stateChangeStatistic()

Update the correct state transition statistic.

- Parameters

-

before The state the line was in before after The new state of the line

Field Documentation

◆ curr_access_addr

|

private |

The address being accessed by the current processor read or write.

- Note

- Remembering the currently accessed address only works because each memory access is atomic, i.e. all resulting bus messages will finish before the next memory access

The documentation for this class was generated from the following files: