Global type definitions. More...

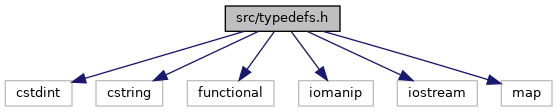

#include <cstdint>#include <cstring>#include <functional>#include <iomanip>#include <iostream>#include <map>

Include dependency graph for typedefs.h:

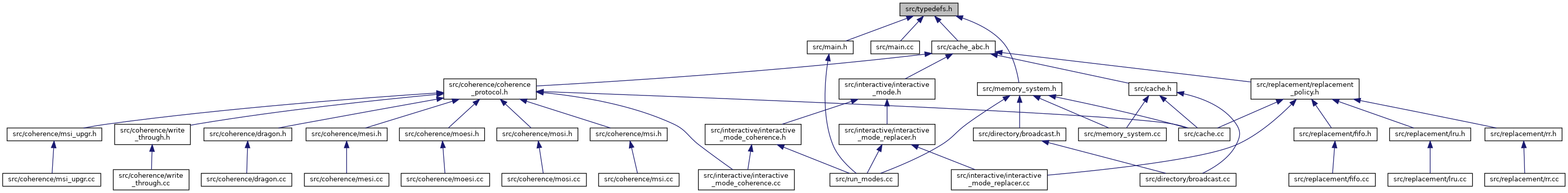

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Data Structures | |

| struct | cache_line |

| Cache line fields (without data field) More... | |

| struct | cache_config |

| Configuration for an individual memory system. More... | |

| struct | ci_less |

| Comparator functor for strings, case insensitive. More... | |

| struct | trace_t |

| The format of a single trace. More... | |

Macros | |

| #define | N_INTERACTIVE_MODE_LINES 5 |

| The number of cache lines that interactive mode uses. | |

Typedefs | |

| typedef uint32_t | addr_t |

| Memory address. | |

| typedef uint32_t | tag_t |

| Cache line tag. | |

| typedef std::function< CoherenceProtocol *(CacheABC &)> | coh_factory_t |

| Coherence protocol factory function signature. | |

| typedef std::function< MemorySystem *(cache_config &)> | dir_factory_t |

| Directory protocol factory function signature. | |

| typedef std::function< ReplacementPolicy *(CacheABC &, uint32_t, uint32_t)> | rep_factory_t |

| Replacement policy factory function signature. | |

Enumerations | |

| enum | args_single_e { ARG_S_PROG , ARG_CACHE_SIZE , ARG_LINE_SIZE , ARG_ASSOCIATIVITY , ARG_COHERENCE , ARG_REPLACEMENT , ARG_DIRECTORY , ARG_C_COUNT , ARG_S_TRACE_FILE = ARG_C_COUNT , ARG_S_TRACE_LIMIT , ARG_S_COUNT } |

| Argument indices for single metrics run. | |

| enum | args_batch_e { ARG_M_PROG , ARG_CONFIG , ARG_M_TRACE_FILE , ARG_M_TRACE_LIMIT , ARG_M_COUNT } |

| Argument indices for multiple metrics run. | |

| enum | args_interactive_e { ARG_I_PROG , ARG_INTERACTIVE , ARG_I_COUNT } |

| Argument indices for interactive mode. | |

| enum | state_e { Unallocated = 0 , I = 0 , D , E , M , V , O , S , Sc , Sm } |

| Cache line state. More... | |

| enum | bus_msg_e { ProcRead , ProcWrite , BusRead , BusReadX , BusUpdate , BusUpgrade , BusWrite , N_MESSAGES } |

| Bus message IDs. More... | |

| enum | statistic_e { ReadMiss = N_MESSAGES , WriteMiss , LineFlush , LineFetch , CacheToCache , WriteBack , WriteMemory , Eviction , Exclusion , Intervention , Invalidation , N_STATISTICS } |

| Cache runtime statistic IDs. More... | |

Variables | |

| std::map< std::string, coh_factory_t, ci_less > * | coherence_map |

| A map from coherence protocol names to their factory functions. | |

| std::map< std::string, dir_factory_t, ci_less > * | directory_map |

| A map from directory protocol names to their factory functions. | |

| std::map< std::string, rep_factory_t, ci_less > * | replacement_map |

| A map from replacement policy names to their factory functions. | |

Detailed Description

Global type definitions.

Enumeration Type Documentation

◆ bus_msg_e

| enum bus_msg_e |

Bus message IDs.

◆ state_e

| enum state_e |

Cache line state.

◆ statistic_e

| enum statistic_e |

Cache runtime statistic IDs.

- Note

- Continuation of 'bus_msg_e'

| Enumerator | |

|---|---|

| ReadMiss | Read miss on a cache line. |

| WriteMiss | Write miss on a cache line. |

| LineFlush | Cache line data broadcasted across memory bus. |

| LineFetch | Cache line data retrieved from main memory. |

| CacheToCache | Transfer between two caches. |

| WriteBack | Cache line data written to main memory. |

| WriteMemory | Direct write from CPU to main memory. |

| Eviction | Cache line evicted by the replacement policy. |

| Exclusion | Cache line changes from shared (O, S, Sc, Sm) to singular (D, E, M, V) |

| Intervention | Cache line changes from singular (D, E, M, V) to shared (O, S, Sc, Sm) |

| Invalidation | Cache line state set to invalid (I) |

| N_STATISTICS | The number of statistics a cache keeps track of; not a statistic. |