The MSI coherence protocol. More...

#include <msi.h>

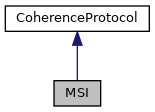

Inheritance diagram for MSI:

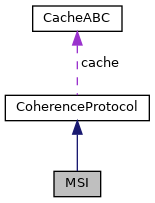

Collaboration diagram for MSI:

Public Member Functions | |

| MSI (CacheABC &cache) | |

| Construct a new MSI coherence protocol. More... | |

| void | PrRd (cache_line *line) |

| Receive a PrRd message. More... | |

| void | PrWr (cache_line *line) |

| Receive a PrWr message. More... | |

| bool | BusRd (cache_line *line) |

| Receive a BusRd message. More... | |

| bool | BusRdX (cache_line *line) |

| Receive a BusRdX message. More... | |

| bool | isWriteBackNeeded (state_e state) |

| Determine whether a line needs to be written back to main memory. More... | |

Public Member Functions inherited from CoherenceProtocol Public Member Functions inherited from CoherenceProtocol | |

| CoherenceProtocol (CacheABC &cache) | |

| Construct a new coherence protocol. More... | |

| virtual bool | BusUpdt (cache_line *line) |

| Receive a BusUpdt message. More... | |

| virtual bool | BusUpgr (cache_line *line) |

| Receive a BusUpgr message. More... | |

| virtual bool | BusWr (cache_line *line) |

| Receive a BusWr message. More... | |

| virtual bool | doesDirtySharing () |

| Determine whether the coherence protocol does dirty sharing. More... | |

| virtual bool | doesWriteNoAllocate () |

| Determine whether the coherence protocol uses write no-allocate. More... | |

Additional Inherited Members | |

Protected Attributes inherited from CoherenceProtocol Protected Attributes inherited from CoherenceProtocol | |

| CacheABC & | cache |

| The parent cache. | |

Detailed Description

The MSI coherence protocol.

Constructor & Destructor Documentation

◆ MSI()

|

inline |

Construct a new MSI coherence protocol.

- Parameters

-

cache The parent cache

Member Function Documentation

◆ BusRd()

|

virtual |

Receive a BusRd message.

- Parameters

-

line The cache line accessed

- Returns

- True if the line data can be or could have been shared

Implements CoherenceProtocol.

◆ BusRdX()

|

virtual |

Receive a BusRdX message.

- Parameters

-

line The cache line accessed

- Returns

- True if the line data can be or could have been shared

Reimplemented from CoherenceProtocol.

◆ isWriteBackNeeded()

|

virtual |

Determine whether a line needs to be written back to main memory.

- Parameters

-

state The state of the line

- Returns

- Whether the line needs to be written back to main memory

Implements CoherenceProtocol.

◆ PrRd()

|

virtual |

Receive a PrRd message.

- Parameters

-

line The cache line accessed (non-null)

Implements CoherenceProtocol.

◆ PrWr()

|

virtual |

Receive a PrWr message.

- Parameters

-

line The cache line accessed (non-null)

Implements CoherenceProtocol.

The documentation for this class was generated from the following files: